mosfet - What is the significance of FO4 inverters in CMOS static circuits? - Electrical Engineering Stack Exchange

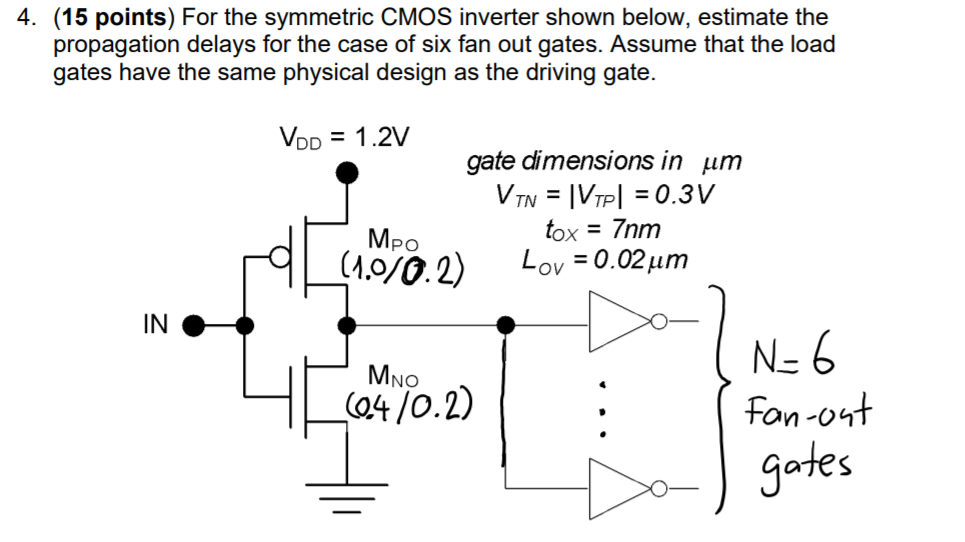

Simulation scheme for CMOS logic gates with input pulse forming and... | Download Scientific Diagram

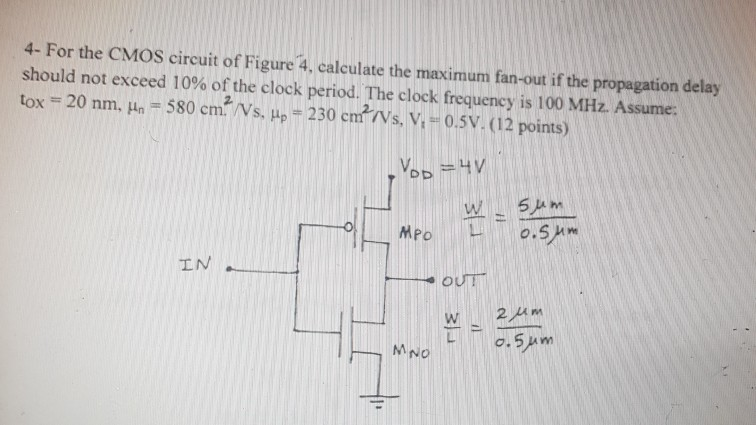

Simulation scheme for CMOS logic gates with input pulse forming and... | Download Scientific Diagram

![The Stuff Dreams Are Made Of [Part 2] The Stuff Dreams Are Made Of [Part 2]](http://www.realworldtech.com/includes/images/articles/cmosintro2-fig3.gif?x56147)